Tranzistory s efektem přechodového pole

Junction Field Effect Tranzistors jsou napěťově řízené tranzistory na bázi polovodičů. Jedná se o jednosměrné tranzistory se třemi vývody; odtok, zdroj a brána. JFETy nemají PN přechody, ale jsou složeny z kanálů z polovodičových materiálů.

Konstrukce a klasifikace

JFETy mají velký kanál pro tok většiny nosičů náboje. Tento kanál je známý jako substrát. Substrát může být z materiálu typu P nebo typu N. Přes dva konce kanálu jsou umístěny dva externí kontakty známé jako ohmické kontakty. JFET jsou klasifikovány na základě polovodičového materiálu substrátu v jejich konstrukci.

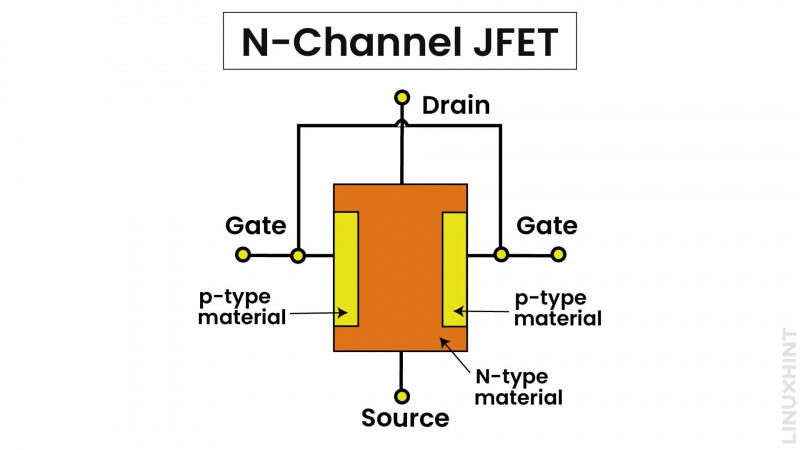

N-kanálové tranzistory JFET

Kanál je vyroben z příměsového materiálu typu N, zatímco hradla jsou složena z příměsového materiálu typu P. Materiál typu N znamená, že pětimocné nečistoty byly dotovány a většinu nosičů náboje tvoří volné elektrony v kanálu. Základní konstrukce a symbolická prezentace N-kanálových JFET je zobrazena níže:

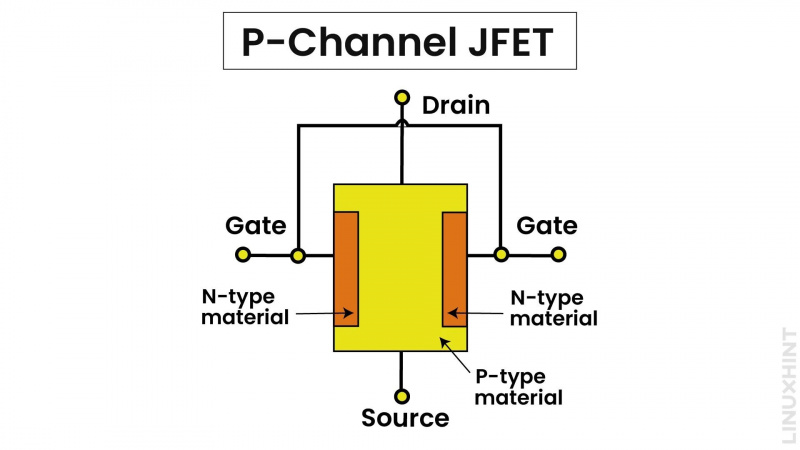

P-kanálové tranzistory JFET

Kanál je složen z příměsového materiálu typu P, zatímco hradla jsou složena z příměsového materiálu typu N. P-Kanál znamená, že v kanálu byly dopovány trojmocné nečistoty a většina nosičů náboje jsou díry. Základní konstrukce a symbolická prezentace P-Channel JFET je uvedena níže:

Fungování JFETů

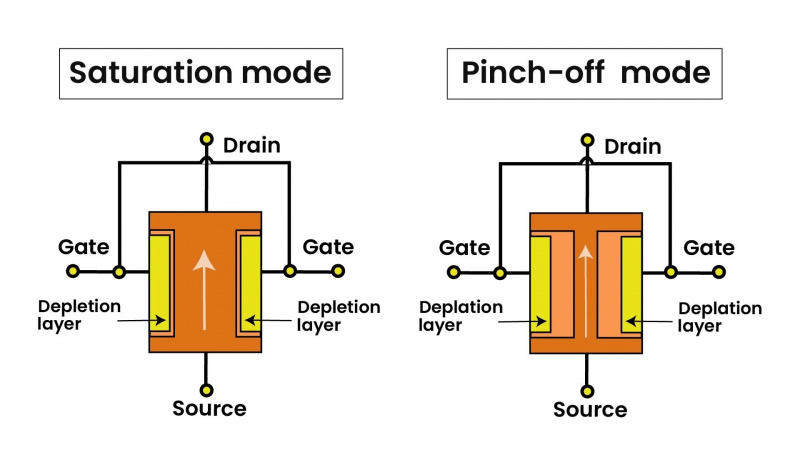

JFETs jsou často popisovány s analogií potrubí vodní hadice. Tok vody potrubím je analogický s tokem elektronů kanály JFET. O množství průtoku vody rozhoduje zmáčknutí vodovodní trubky. Podobně v případě JFETů rozhoduje o zúžení nebo rozšíření kanálu pro pohyb nábojů od zdroje k odtoku aplikace napětí přes hradlové terminály.

Když je aplikováno zpětné předpětí přes hradlo a zdroj, kanál se zužuje, zatímco vrstva vyčerpání se zvyšuje. Tento provozní režim se nazývá režim pinch-off. Tento druh chování kanálu je znázorněn níže:

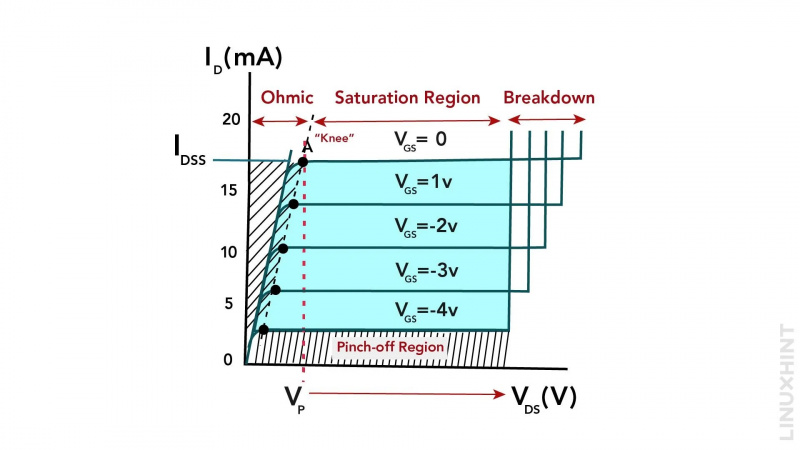

Charakteristická křivka JFET

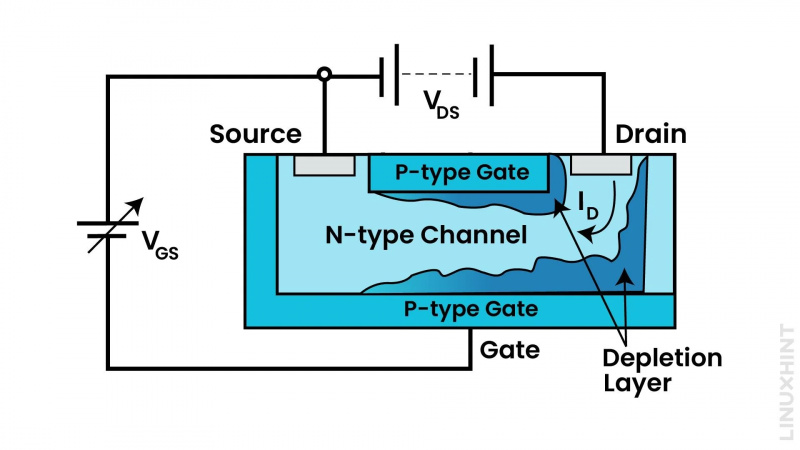

JFET jsou zařízení v režimu vyčerpání, což znamená, že fungují na rozšiřování nebo zužování vrstev vyčerpání. Pro analýzu kompletních provozních režimů se na N-kanálový JFET použije následující uspořádání předpětí.

Na svorky JFET jsou aplikována dvě různá předpětí. VDS se aplikuje mezi odtok a zdroj, zatímco VGS se aplikuje mezi hradlem a zdrojem, jak je znázorněno na obrázku výše.

JFET bude fungovat ve čtyřech různých režimech provozu, jak je diskutováno níže.

1: Ohmický režim

Ohmický režim je normální stav bez jakéhokoli předpětí na jeho svorkách. Proto VGS=0 v ohmickém režimu. Depleční vrstva musí být velmi tenká a JFET funguje jako ohmický prvek, jako je rezistor.

2: Režim Pinch-Off

V režimu cut-off je aplikováno dostatečné předpětí přes hradlo a zdroj. Aplikované zpětné předpětí natáhne oblast vyčerpání na maximální úroveň, a proto se kanál chová jako otevřený spínač, který brání toku proudu.

3: Režim sytosti

Předpětí brány a zdroje řídí tok proudu kanálem JFET. Proud se mění se změnou předpětí. Odběrové a zdrojové předpětí má v tomto režimu zanedbatelný vliv.

4: Režim rozdělení

Odběrové a zdrojové předpětí se zvýší na úroveň, která naruší vrstvu vyčerpání v kanálu JFET. To vede k maximálnímu průtoku proudu kanálem.

Matematické výrazy pro parametry JFETs

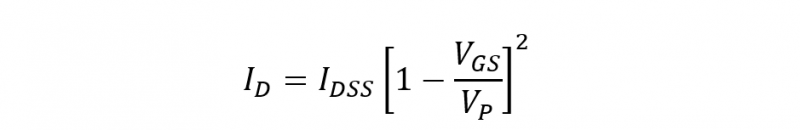

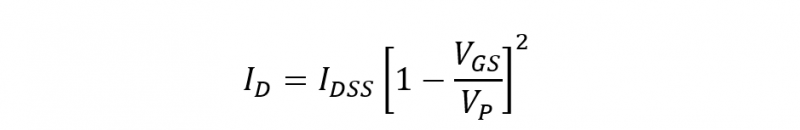

V saturačních režimech vstupují JFETy do režimů vodičů, kde napětí mění proud. Proto lze vyhodnotit odvodňovací proud. Výraz pro vyhodnocení odtokového proudu je dán vztahem:

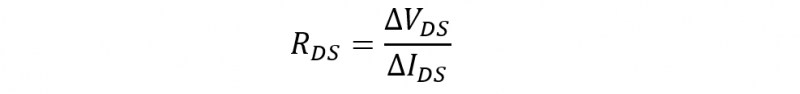

Kanál se rozšiřuje nebo zužuje při použití hradlového napětí. Odpor kanálu vzhledem k aplikaci napětí zdroje kolektoru je vyjádřen jako:

RDS lze také vypočítat pomocí transkonduktančního zisku, gm:

Konfigurace JFET

JFETy mohou být připojeny různými způsoby se vstupním napětím. Tyto konfigurace jsou známé jako konfigurace společného zdroje, společné brány a společného odtoku.

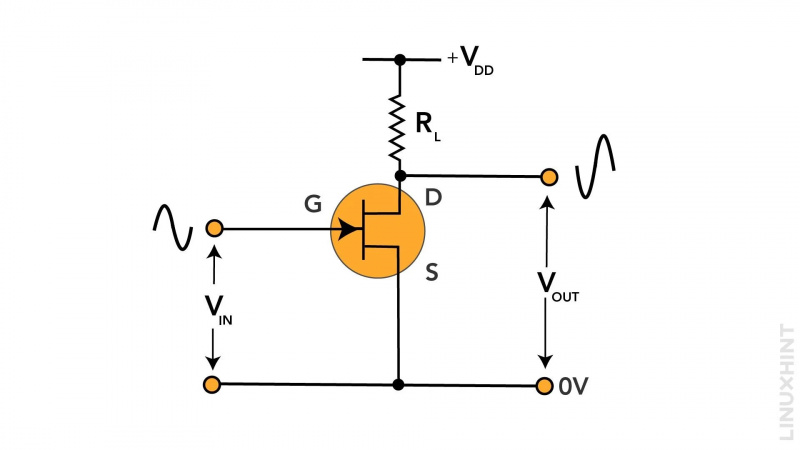

Konfigurace společného zdroje

V běžné konfiguraci zdroje je zdroj JFET uzemněn a vstup je připojen ke svorce hradla, zatímco výstup je odebírán z kolektoru. Tato konfigurace nabízí vysokou vstupní impedanci a funkce zesílení napětí. Tato konfigurace režimu zesilovače je nejběžnější ze všech konfigurací JFET. Získaný výstup je fázově posunutý o 180 stupňů vůči vstupu.

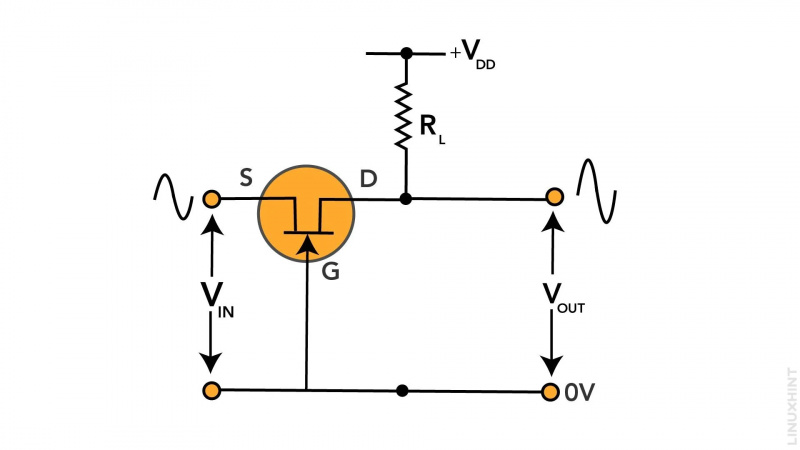

Konfigurace společné brány

V běžné konfiguraci hradla je hradlo uzemněno, zatímco vstup je připojen ke zdroji a výstup je odebírán ze svodu. Jelikož je hradlo spojeno se zemí, konfigurace má nízkou vstupní impedanci, ale vyšší impedanci na výstupu. Získaný výstup je ve fázi se vstupem:

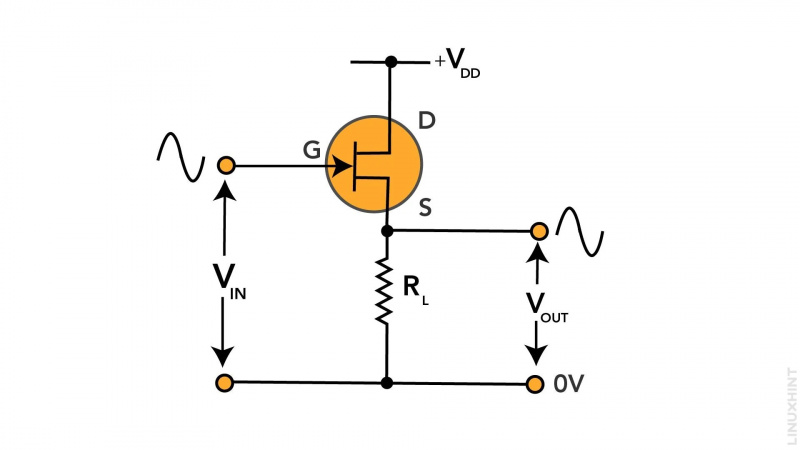

Konfigurace společného odtoku

Ve společném kolektoru je vstup připojen k bráně, zatímco výstup je připojen ke zdrojové svorce. Tato konfigurace také nabízí nízkou vstupní impedanci a vyšší výstupní impedanci stejně jako běžná konfigurace hradla, ale napěťový zisk je zde přibližně jednotný.

Tato konfigurace také odpovídá běžnému zdroji, kde je vstup připojen k bráně, ale konfigurace společného zdroje má zisk menší než jednota.

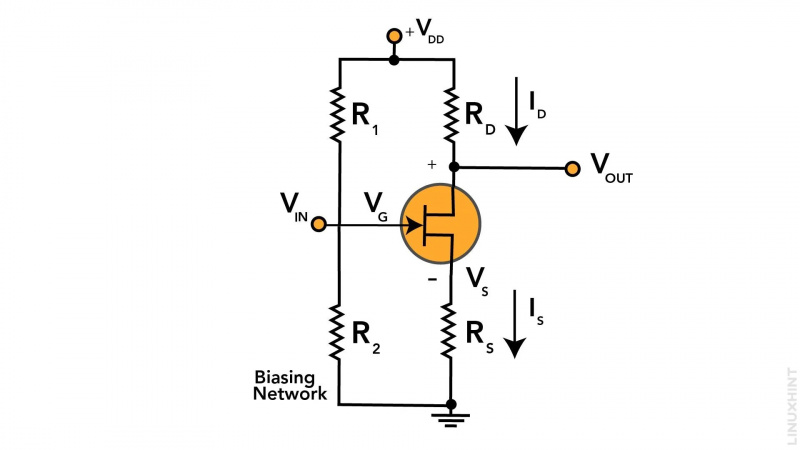

Aplikace – Konfigurace zesilovače JFET

JFETy mohou fungovat jako zesilovače třídy A, když je hradlový terminál spojen se sítí děliče napětí. Externí napětí je přivedeno na svorku zdroje, která je většinou nakonfigurována na jednu čtvrtinu VDD v níže uvedeném obvodu.

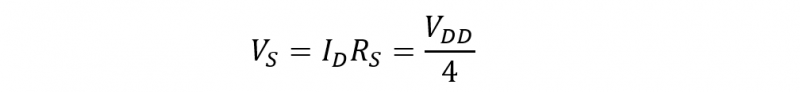

Zdrojové napětí lze tedy vyjádřit jako:

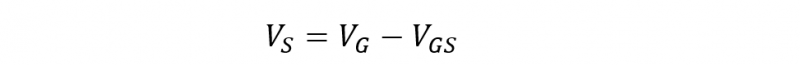

Zdrojové napětí lze také vypočítat pomocí níže uvedeného výrazu:

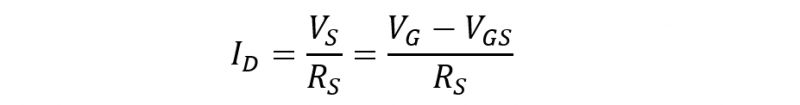

Odtokový proud lze vypočítat z výše uvedené konfigurace, jak je uvedeno níže:

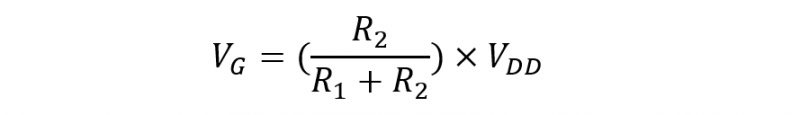

Napětí hradla lze získat jako funkci hodnot rezistorů R1 a R2, jak je uvedeno níže.

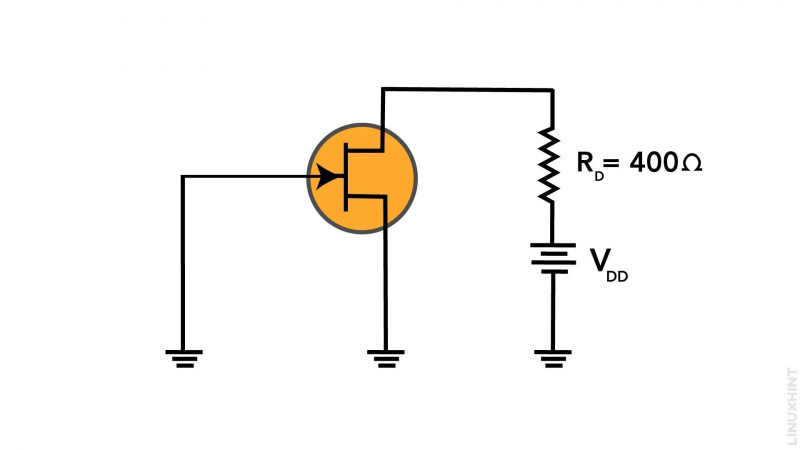

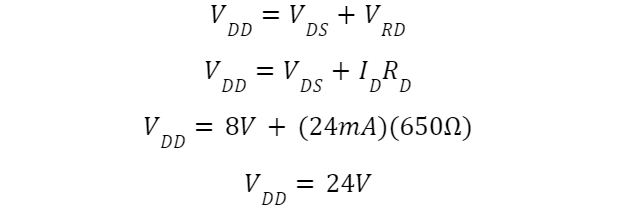

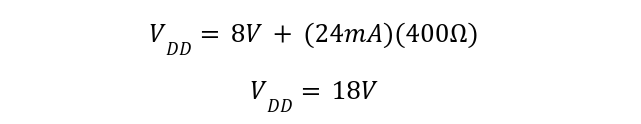

Příklad 1: Výpočet V DD

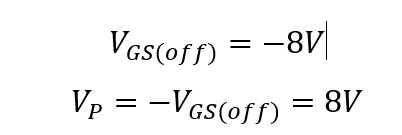

Pokud V GS(vypnuto) =-8V, I DSS =24mA pro JFET v níže uvedené konfiguraci, vypočítejte V DD jak je znázorněno na obrázku, když R D = 400.

Od té doby

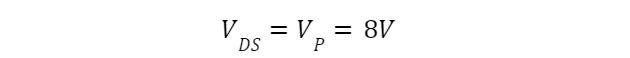

Výše uvedené bude minimální hodnotou VDS pro provoz JFET v oblasti konstantního proudu, proto:

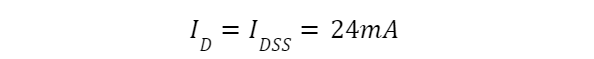

Taky,

Použitím KVL na odtokovém okruhu:

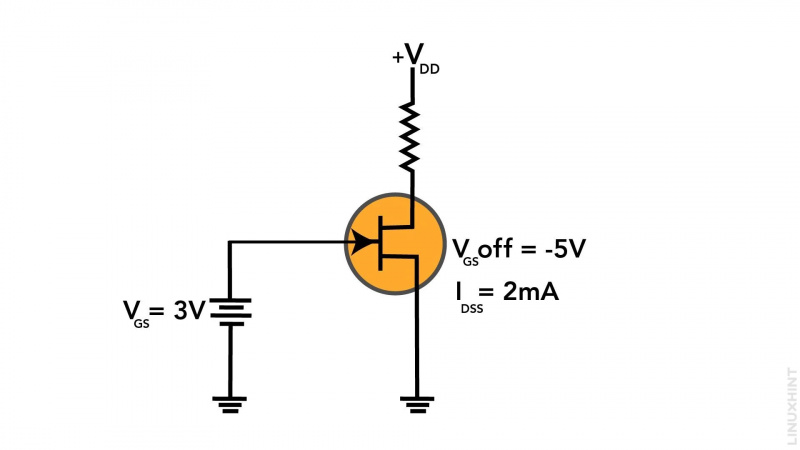

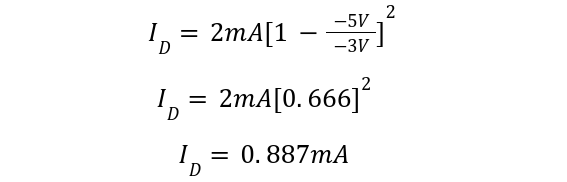

Příklad 2: Určete hodnotu vypouštěcího proudu

Určete hodnotu odběrového proudu, když VGS=3V, VGS(Off)=-5V, IDSS=2mA pro konfiguraci pod JFET.

Výraz pro odtokový proud je:

Závěr

Junction Field Effect Tranzistors jsou tři koncová polovodičová zařízení, která pracují s chováním oblastí vyčerpání v různých režimech provozu. Nemají PN přechody, ale jsou vyrobeny z kanálků z polovodičových materiálů.